- Hardware & Machines

- Computers and Hardware

- LinuxCNC-RIO - RealtimeIO for LinuxCNC based on FPGA (ICE40 / ECP5)

LinuxCNC-RIO - RealtimeIO for LinuxCNC based on FPGA (ICE40 / ECP5)

- epineh

- Offline

- Senior Member

-

Less

More

- Posts: 75

- Thank you received: 27

11 Jun 2025 12:28 #330141

by epineh

Replied by epineh on topic LinuxCNC-RIO - RealtimeIO for LinuxCNC based on FPGA (ICE40 / ECP5)

Look forward to seeing how that goes, Tang Nano's are about 30 bucks AUD, two of them are still cheaper than any FPGA with a similar total pincount. I'm being selfish but that also means I stick with the same FPGA hardware for every machine I can possibly imagine making.

Let me know if I can help with testing, I'm currently retrofitting my three machines to closed loop to the controller, so there's room for some hardware experimentation.

Let me know if I can help with testing, I'm currently retrofitting my three machines to closed loop to the controller, so there's room for some hardware experimentation.

Please Log in or Create an account to join the conversation.

- meister

- Offline

- Platinum Member

-

Less

More

- Posts: 728

- Thank you received: 443

11 Jun 2025 12:32 #330143

by meister

Replied by meister on topic LinuxCNC-RIO - RealtimeIO for LinuxCNC based on FPGA (ICE40 / ECP5)

if you have two (or more  ) Tangnano, you can try it, you need the 'dev' branch and

) Tangnano, you can try it, you need the 'dev' branch and

2 free pins on each tangnano (RX / TX).

For short distance, you connect this pins direct (RX<->TX) or using RS485/RS422 converter for long distance.

2 free pins on each tangnano (RX / TX).

For short distance, you connect this pins direct (RX<->TX) or using RS485/RS422 converter for long distance.

Please Log in or Create an account to join the conversation.

- epineh

- Offline

- Senior Member

-

Less

More

- Posts: 75

- Thank you received: 27

12 Jun 2025 11:48 #330203

by epineh

Replied by epineh on topic LinuxCNC-RIO - RealtimeIO for LinuxCNC based on FPGA (ICE40 / ECP5)

Oh wait a minute, so you can have more than one extra FPGA? Alright then looks like I need to order some more Tang's.

The following user(s) said Thank You: meister

Please Log in or Create an account to join the conversation.

- meister

- Offline

- Platinum Member

-

Less

More

- Posts: 728

- Thank you received: 443

12 Jun 2025 11:57 #330204

by meister

Replied by meister on topic LinuxCNC-RIO - RealtimeIO for LinuxCNC based on FPGA (ICE40 / ECP5)

yes, but please try it first, it's experimental !

Please Log in or Create an account to join the conversation.

- meister

- Offline

- Platinum Member

-

Less

More

- Posts: 728

- Thank you received: 443

13 Jun 2025 19:24 #330258

by meister

Replied by meister on topic LinuxCNC-RIO - RealtimeIO for LinuxCNC based on FPGA (ICE40 / ECP5)

github.com/multigcs/riocore/blob/dev/doc/RIOSUB.md

I think I need a different name for it

suggestions are welcome !

I think I need a different name for it

suggestions are welcome !

Please Log in or Create an account to join the conversation.

- epineh

- Offline

- Senior Member

-

Less

More

- Posts: 75

- Thank you received: 27

15 Jun 2025 10:33 #330302

by epineh

Replied by epineh on topic LinuxCNC-RIO - RealtimeIO for LinuxCNC based on FPGA (ICE40 / ECP5)

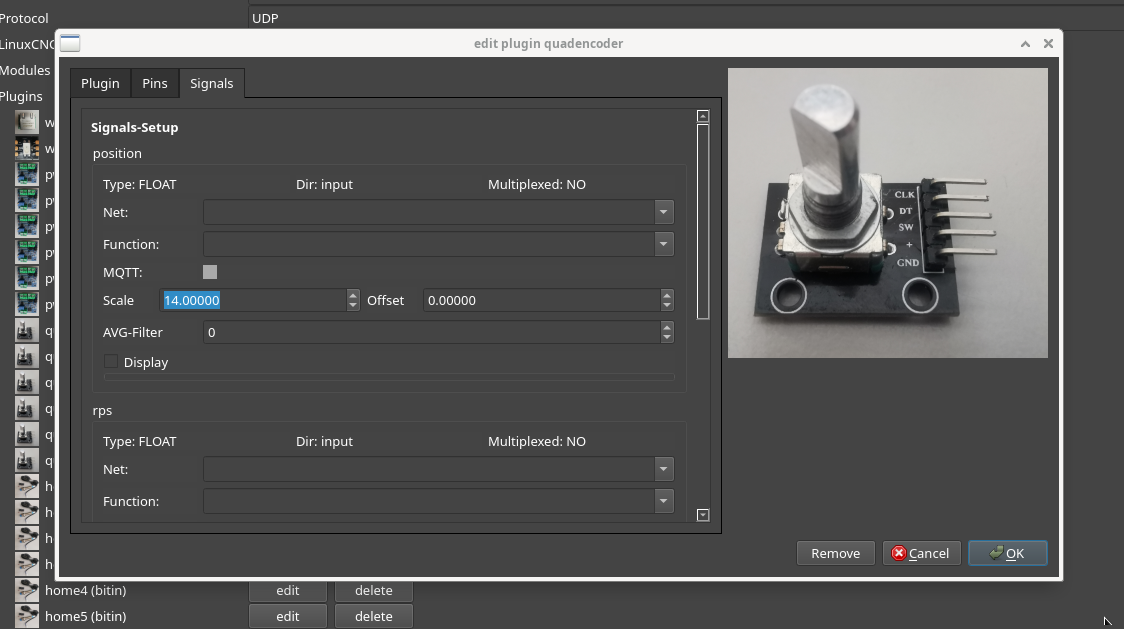

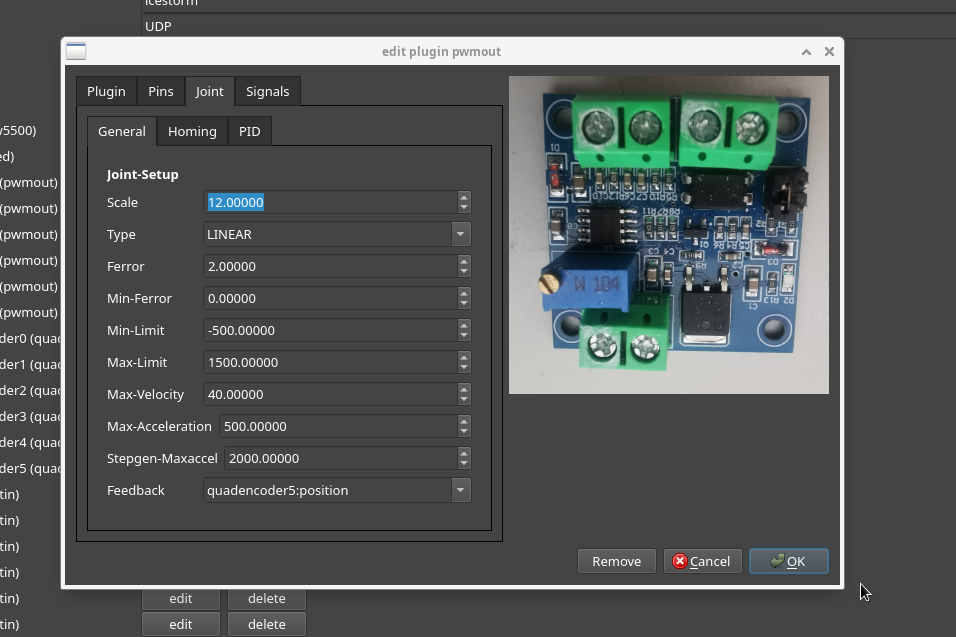

Quick question hopefully, I'm setting up my router with closed loop to the controller, apart from getting the scale right it's all working, my question is when you setup the scale in the pwm/dir config, it sets up the axis "scale in" to that, but leaves the scale out value at 1 or zero (can't remember exactly). At this value the axis will run away similar to having the encoder wires around the wrong way.

I can set it using the machine calibrate window within Linuxcnc but it gets overwritten every time setup is run. Then if you forget about it and an axis is close to end of travel, bad things can happen.

I've most likely just missed where to put in the scale out value but I can't seem to find it.

Cheers.

Russell.

I can set it using the machine calibrate window within Linuxcnc but it gets overwritten every time setup is run. Then if you forget about it and an axis is close to end of travel, bad things can happen.

I've most likely just missed where to put in the scale out value but I can't seem to find it.

Cheers.

Russell.

Please Log in or Create an account to join the conversation.

- meister

- Offline

- Platinum Member

-

Less

More

- Posts: 728

- Thank you received: 443

16 Jun 2025 05:32 #330333

by meister

Replied by meister on topic LinuxCNC-RIO - RealtimeIO for LinuxCNC based on FPGA (ICE40 / ECP5)

Attachments:

Please Log in or Create an account to join the conversation.

- epineh

- Offline

- Senior Member

-

Less

More

- Posts: 75

- Thank you received: 27

16 Jun 2025 08:04 #330335

by epineh

Replied by epineh on topic LinuxCNC-RIO - RealtimeIO for LinuxCNC based on FPGA (ICE40 / ECP5)

Ahh awesome thanks.

Please Log in or Create an account to join the conversation.

- DMNZ

- Offline

- Junior Member

-

Less

More

- Posts: 25

- Thank you received: 8

19 Jun 2025 01:17 #330476

by DMNZ

Replied by DMNZ on topic LinuxCNC-RIO - RealtimeIO for LinuxCNC based on FPGA (ICE40 / ECP5)

I've been looking into RIO for couple of days, reading forums and one question i can't find the answer for, may be it is obvious for all but me, what is the data protocol used in RIO over the spi? is it the same as Mesa LBP16 commands requiring hostmot2 or something else?

Please Log in or Create an account to join the conversation.

- meister

- Offline

- Platinum Member

-

Less

More

- Posts: 728

- Thank you received: 443

19 Jun 2025 09:44 #330495

by meister

Replied by meister on topic LinuxCNC-RIO - RealtimeIO for LinuxCNC based on FPGA (ICE40 / ECP5)

there is no real protocol,

it is a frame with a fixed length (depending on the config) in which all necessary data is sent and received in byte blocks.

Here is an example of the default Tangbob config:

the frames are then filled with zeros so that they are always divisible by 8 bits and RX and TX frames have the same length so that they can be transmitted via SPI full duplex

a hal component (riocomp.c) is also generated for each config, which can read and write the frames and, if necessary, does a few floating point calculations that I wanted to keep away from the FPGA

This makes it possible to manage without SoftCore in the FPGA, i.e. only pure logic

it is a frame with a fixed length (depending on the config) in which all necessary data is sent and received in byte blocks.

Here is an example of the default Tangbob config:

cat Output/Tangbob/DOC/INTERFACE.md

# Interface

## Host to FPGA

| POS | SIZE | NAME |

| --- | --- | --- |

| 0 | 32bits | RX_HEADER |

| 32 | 128bits | VAROUT128_MODBUS0_TXDATA |

| 160 | 32bits | VAROUT32_PWMOUT0_DTY |

| 192 | 32bits | VAROUT32_STEPDIR0_VELOCITY |

| 224 | 32bits | VAROUT32_STEPDIR1_VELOCITY |

| 256 | 32bits | VAROUT32_STEPDIR2_VELOCITY |

| 288 | 32bits | VAROUT32_STEPDIR3_VELOCITY |

| 320 | 1bit | VAROUT1_WLED0_0_GREEN |

| 321 | 1bit | VAROUT1_WLED0_0_BLUE |

| 322 | 1bit | VAROUT1_WLED0_0_RED |

| 323 | 1bit | VAROUT1_BITOUT0_BIT |

| 324 | 1bit | VAROUT1_BITOUT1_BIT |

| 325 | 1bit | VAROUT1_PWMOUT0_ENABLE |

| 326 | 1bit | VAROUT1_STEPDIR0_ENABLE |

| 327 | 1bit | VAROUT1_STEPDIR1_ENABLE |

| 328 | 1bit | VAROUT1_STEPDIR2_ENABLE |

| 329 | 1bit | VAROUT1_STEPDIR3_ENABLE |

## FPGA to Host

| POS | SIZE | NAME |

| --- | --- | --- |

| 0 | 32bits | TX_HEADER |

| 32 | 32bits | TIMESTAMP |

| 64 | 16bits | MULTIPLEXED_INPUT_VALUE |

| 80 | 8bits | MULTIPLEXED_INPUT_ID |

| 88 | 128bits | VARIN128_MODBUS0_RXDATA |

| 216 | 32bits | VARIN32_STEPDIR0_POSITION |

| 248 | 32bits | VARIN32_STEPDIR1_POSITION |

| 280 | 32bits | VARIN32_STEPDIR2_POSITION |

| 312 | 32bits | VARIN32_STEPDIR3_POSITION |

| 344 | 1bit | VARIN1_BITIN0_BIT |

| 345 | 1bit | VARIN1_BITIN1_BIT |

| 346 | 1bit | VARIN1_BITIN2_BIT |

| 347 | 1bit | VARIN1_BITIN3_BIT |

| 348 | 1bit | VARIN1_BITIN4_BIT |

the frames are then filled with zeros so that they are always divisible by 8 bits and RX and TX frames have the same length so that they can be transmitted via SPI full duplex

a hal component (riocomp.c) is also generated for each config, which can read and write the frames and, if necessary, does a few floating point calculations that I wanted to keep away from the FPGA

This makes it possible to manage without SoftCore in the FPGA, i.e. only pure logic

Please Log in or Create an account to join the conversation.

- Hardware & Machines

- Computers and Hardware

- LinuxCNC-RIO - RealtimeIO for LinuxCNC based on FPGA (ICE40 / ECP5)

Time to create page: 0.275 seconds