ColorCNC Colorlight 5A-75E/5A-75B as FPGA controller board

- vit74vit

- Offline

- New Member

-

Less

More

- Posts: 14

- Thank you received: 4

13 Aug 2022 11:28 - 15 Aug 2022 08:53 #249642

by vit74vit

Replied by vit74vit on topic ColorCNC Colorlight 5A-75E/5A-75B as FPGA controller board

Problem: sizeof(litexcnc_stepgen_general_write_data_t) return 24typedef struct { uint32_t steplen; uint32_t dir_hold_time; uint32_t dir_setup_time; uint64_t apply_time;} litexcnc_stepgen_general_write_data_t;PS: Aligning structures results in an error. The incorrect read/write buffer length was caused by this. Updated stepgen.h file. I continue to test.

Last edit: 15 Aug 2022 08:53 by vit74vit.

The following user(s) said Thank You: TOLP2

Please Log in or Create an account to join the conversation.

- TOLP2

- Offline

- Elite Member

-

Less

More

- Posts: 225

- Thank you received: 178

13 Aug 2022 19:35 - 13 Aug 2022 20:31 #249674

by TOLP2

Replied by TOLP2 on topic ColorCNC Colorlight 5A-75E/5A-75B as FPGA controller board

How can it be that the sizeof return 24, I do really count only 20 bytes ... But this explains why it does work on my system (32-bit), because this architecture is quiet becoming obsolete, I think you use 64-bit architectures.

So either I have to replace all sizeof with macros or find a way to make it portable between the architetures. My gratitude for solving this problem is huge...

Edit: I've just committed a modified version of the driver. I've replaced all occurrences of 'sizeof' with hardcoded sizes of the read and write data-structs.

So either I have to replace all sizeof with macros or find a way to make it portable between the architetures. My gratitude for solving this problem is huge...

Edit: I've just committed a modified version of the driver. I've replaced all occurrences of 'sizeof' with hardcoded sizes of the read and write data-structs.

Last edit: 13 Aug 2022 20:31 by TOLP2. Reason: Update

Please Log in or Create an account to join the conversation.

- vit74vit

- Offline

- New Member

-

Less

More

- Posts: 14

- Thank you received: 4

14 Aug 2022 06:04 #249698

by vit74vit

Replied by vit74vit on topic ColorCNC Colorlight 5A-75E/5A-75B as FPGA controller board

Peter!

137 line in stepgen.h should be modifed :

stepgen.num_instances?sizeof(litexcnc_stepgen_general_write_data_t):0)

stepgen.num_instances?20:0)

PS:I don't like to use "magic number".

I propose to use forced alignment during packaging

#pragma pack(push,4)

...... structure.....

#pragma pack(pop)

137 line in stepgen.h should be modifed :

stepgen.num_instances?sizeof(litexcnc_stepgen_general_write_data_t):0)

stepgen.num_instances?20:0)

PS:I don't like to use "magic number".

I propose to use forced alignment during packaging

#pragma pack(push,4)

...... structure.....

#pragma pack(pop)

Please Log in or Create an account to join the conversation.

- vit74vit

- Offline

- New Member

-

Less

More

- Posts: 14

- Thank you received: 4

14 Aug 2022 14:32 - 14 Aug 2022 14:37 #249716

by vit74vit

Replied by vit74vit on topic ColorCNC Colorlight 5A-75E/5A-75B as FPGA controller board

Peter, see this example:

struct Foo

{

char ch;

int value;

};

struct Foo1

{

char ch1;

char ch2;

int value1;

};

#pragma pack(push,1)

struct Foo3

{

char ch3;

int value3;

};

#pragma pack(pop)

result out:

sizeof(Foo )=8 (bytes of memmory: 1-ch 2-empty 3-empty 4-empty 5-value[0] 6-value[1] 7-value[2] 8-value[3])

sizeof(Foo1)=8

sizeof(Foo3)=5 (bytes of memmory: 1-ch 2-value[0] 3-value[1] 4-value[2] 5-value[3])

struct Foo

{

char ch;

int value;

};

struct Foo1

{

char ch1;

char ch2;

int value1;

};

#pragma pack(push,1)

struct Foo3

{

char ch3;

int value3;

};

#pragma pack(pop)

result out:

sizeof(Foo )=8 (bytes of memmory: 1-ch 2-empty 3-empty 4-empty 5-value[0] 6-value[1] 7-value[2] 8-value[3])

sizeof(Foo1)=8

sizeof(Foo3)=5 (bytes of memmory: 1-ch 2-value[0] 3-value[1] 4-value[2] 5-value[3])

Last edit: 14 Aug 2022 14:37 by vit74vit.

Please Log in or Create an account to join the conversation.

- romanetz

- Offline

- Senior Member

-

Less

More

- Posts: 47

- Thank you received: 34

14 Aug 2022 16:08 #249729

by romanetz

Replied by romanetz on topic ColorCNC Colorlight 5A-75E/5A-75B as FPGA controller board

Pay attention that etherbone protocol requires 4-byte alignment

Please Log in or Create an account to join the conversation.

- TOLP2

- Offline

- Elite Member

-

Less

More

- Posts: 225

- Thank you received: 178

14 Aug 2022 19:36 #249734

by TOLP2

Replied by TOLP2 on topic ColorCNC Colorlight 5A-75E/5A-75B as FPGA controller board

@romanetz: The problem is the difference in packing required for etherbone (4-byte) and the packing used by x64-systems. As I had only 32-bit system, the alignement was correct by chance. On 64-bit systems the width is 8 byte and then things go wrong.

@vit74vit: Thanks for spotting the last missed sizeof in the stepgen header and for the examples on packing. I think there are two ways forward from here:

- replace the magic variables with macro's and store these close to the structs.

- change the packing. However this might impact the speed of the driver. Do you know what the impact is and whether it is acceptable?

@vit74vit: Thanks for spotting the last missed sizeof in the stepgen header and for the examples on packing. I think there are two ways forward from here:

- replace the magic variables with macro's and store these close to the structs.

- change the packing. However this might impact the speed of the driver. Do you know what the impact is and whether it is acceptable?

Please Log in or Create an account to join the conversation.

- svb

- Offline

- Senior Member

-

Less

More

- Posts: 44

- Thank you received: 10

14 Aug 2022 23:43 - 14 Aug 2022 23:57 #249745

by svb

Replied by svb on topic ColorCNC Colorlight 5A-75E/5A-75B as FPGA controller board

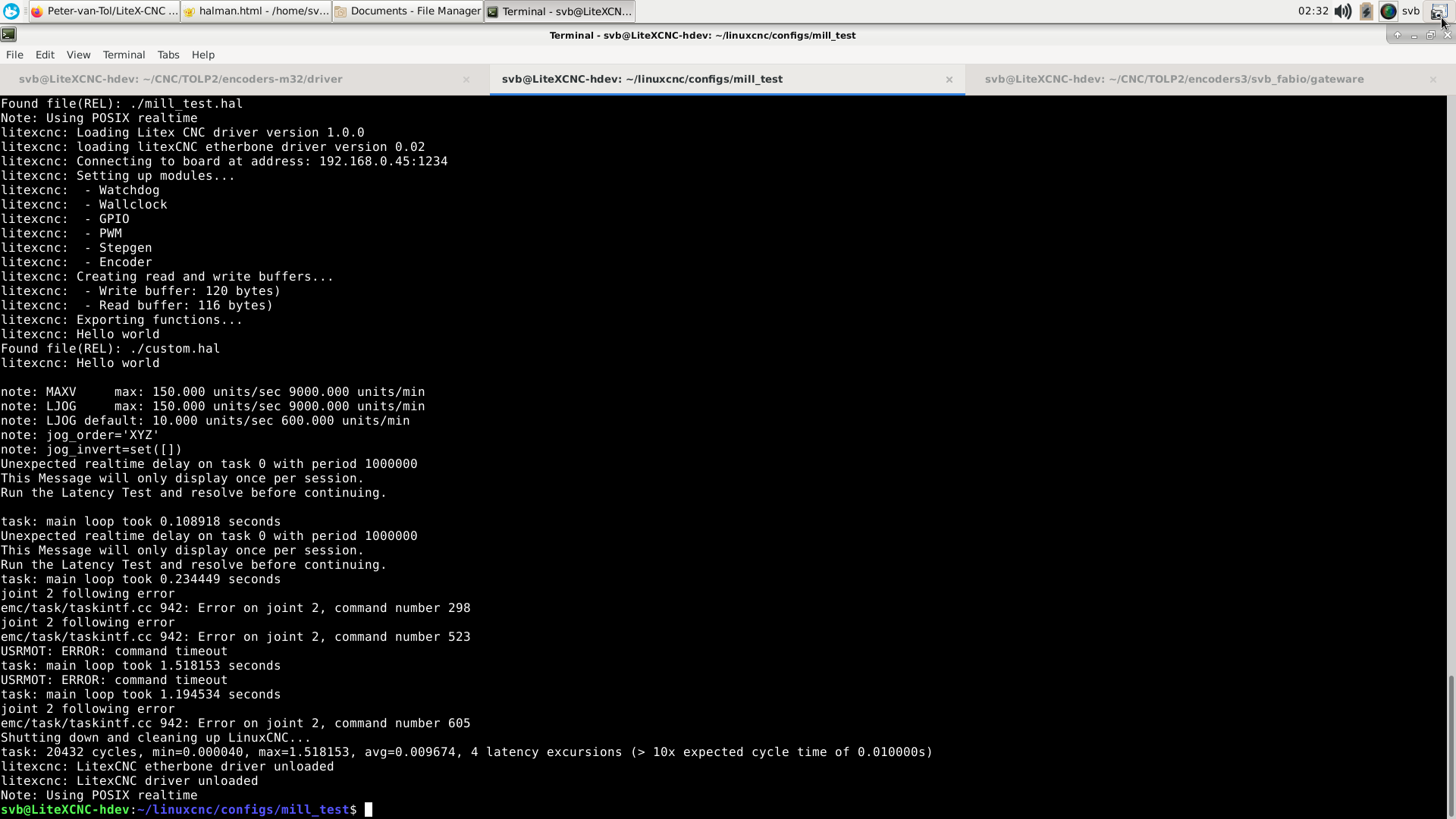

Attachments:

Last edit: 14 Aug 2022 23:57 by svb.

Please Log in or Create an account to join the conversation.

- svb

- Offline

- Senior Member

-

Less

More

- Posts: 44

- Thank you received: 10

14 Aug 2022 23:50 - 14 Aug 2022 23:55 #249747

by svb

Replied by svb on topic ColorCNC Colorlight 5A-75E/5A-75B as FPGA controller board

With Fabio's driver and firmware everything works fine if there is no ethernet packet loss. More than 4 hours of continuous operation without a single failure. I'm run flood ping to board from 3 terminals and all work fine.

I'm connect motors on Y, and test on real hardware.

From time to time packet's lost (i'm don't know why) and all stopped. But NO MOVING after error!

I'm connect motors on Y, and test on real hardware.

From time to time packet's lost (i'm don't know why) and all stopped. But NO MOVING after error!

Last edit: 14 Aug 2022 23:55 by svb.

Please Log in or Create an account to join the conversation.

- romanetz

- Offline

- Senior Member

-

Less

More

- Posts: 47

- Thank you received: 34

15 Aug 2022 06:01 - 15 Aug 2022 06:05 #249755

by romanetz

Replied by romanetz on topic ColorCNC Colorlight 5A-75E/5A-75B as FPGA controller board

Can you point to these versions?

Standard behaviour of of-the-shelf products is to ignore packet loss until timeout has been occured. Loss of packet must only be counted for link quality metering.

Standard behaviour of of-the-shelf products is to ignore packet loss until timeout has been occured. Loss of packet must only be counted for link quality metering.

Last edit: 15 Aug 2022 06:05 by romanetz.

Please Log in or Create an account to join the conversation.

- svb

- Offline

- Senior Member

-

Less

More

- Posts: 44

- Thank you received: 10

15 Aug 2022 13:01 #249780

by svb

Replied by svb on topic ColorCNC Colorlight 5A-75E/5A-75B as FPGA controller board

Fabio set here github.com/faeboli/Lcnc

Please Log in or Create an account to join the conversation.

Moderators: PCW, jmelson

Time to create page: 0.365 seconds